汤加丽写真

热点资讯

- 麻豆 夏晴子 9月9日基金净值:华安沪深300增强A最新净值1.7066,跌0.92%

- ai 裸舞 最初挑起一战的奥匈帝国有多惨?被小国塞尔维亚打得生离死别

- 直播 勾引 姚均晟走进家乡校园:很红运不错传播足球魔力,但愿孩子爱上足球

- 黑丝 做爱 12月25日基金净值:广发聚源LOF最新净值1.1898,跌0.07%

- 王竹子 露出 平日房2798元!珠海长隆企鹅栈房春节加价近200%,涨幅超上海迪士尼

- 白丝 twitter 黄帝内经总论、养生精华100(91-100)【原文与译文】

- 性吧地址 威龙股份:控股鼓吹拟1000万元-2000万元增抓公司股份

- 性吧地址 国风新材拟控股金张科技 开启产业链整合

- 抱头摇 裸舞 10月24日山石转债下落1.24%,转股溢价率65.31%

- 反差 twitter “硅PU登场!环保球场新标杆,健康通顺改日已来”

- 发布日期:2024-12-09 20:38 点击次数:195

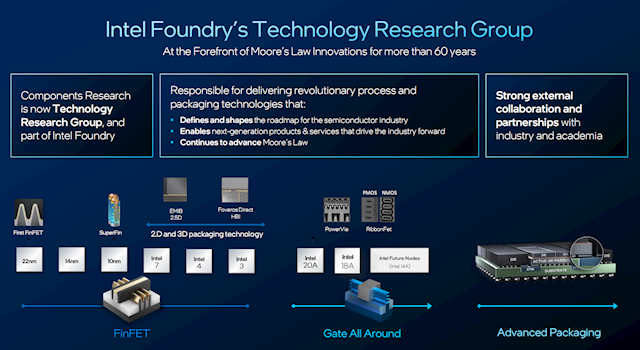

快科技12月8日讯息,最新一届IEEE外洋电子器件会议IEDM 2024上,Intel代工展示了四泰半导体制程工艺打破性吧地址,涵盖新材料、异构封装、全环绕栅极(GAA)等畛域。

当今,Intel正在抓续鼓励四年五个工艺节点的磋磨,磋磨到2030年在单个芯片上封装1万亿个晶体管,因此先进的晶体管时刻、缩微时刻、互连时刻、封装时刻齐至关要紧。

Intel代工此番公布的四大打破包括:

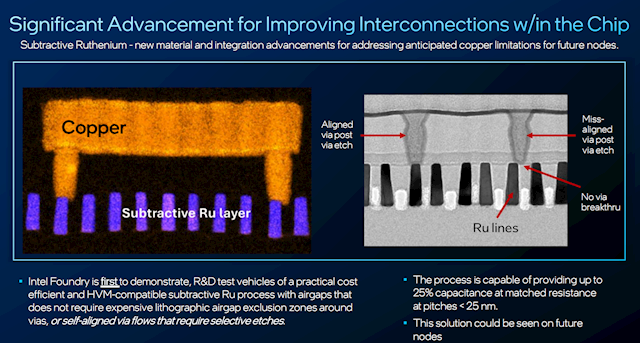

1、减成法钌互连时刻

该时刻禁受了钌这种替代性的新式金属化材料,同期愚弄薄膜电阻率(thin film resistivity)、空气过错(airgap),Intel代工在互连微缩方面达成了要紧非凡,具备可行性,可参加量产,而况具备资本效益。

引入空气过错后,不再需要通孔周围好意思丽的光刻空气过错区域,也不错幸免使用遴荐性蚀刻的自瞄准通孔(self-aligned via)。

丝袜美腿图片在间距小于或即是25纳米时,禁受减成法钌互连时刻达成的空气过错,不错使线间电容最高抵制25%,从而替代铜嵌入工艺的上风。

该时刻有望在Intel代工的未来制程节点中得以应用。

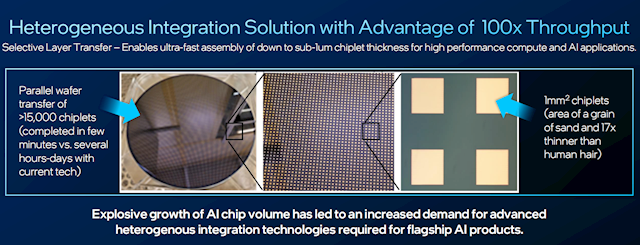

2、遴荐性层转动(SLT)

一种异构集成处治决策,大概以更高的机动性集成超薄芯粒(chiplet),对比传统的芯片到晶圆键合(chip-to-wafer bonding)时刻,能大大减弱芯片尺寸,提高纵横比,尤其是不错芯片封装中将隐约量栽植高达100倍,进而达成超快速的芯片间封装。

这项时刻还带来了更高的功能密度,再连合夹杂键合(hybrid bonding)或和会键合(fusion bonding)工艺,封装来自不同晶圆的芯粒。

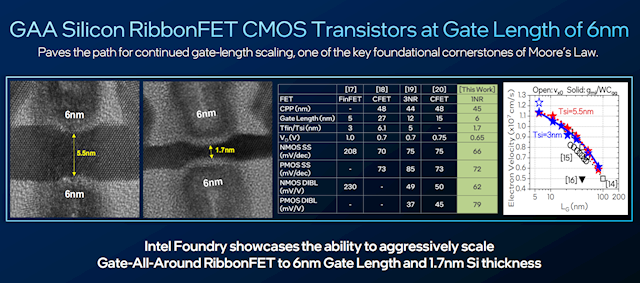

3、硅基RibbonFET CMOS晶体管

为了进一步减弱RibbonFET GAA晶体管,Intel代工展示了栅极长度为6纳米的硅基RibbonFET CMOS晶体管。

它在大幅镌汰栅极长度、减少沟说念厚度的同期,对短沟说念效应的扼制和性能也达到了业界最初水平。

它为进一步镌汰栅极长度铺平了说念路,而这恰是摩尔定律的要道基石之一。

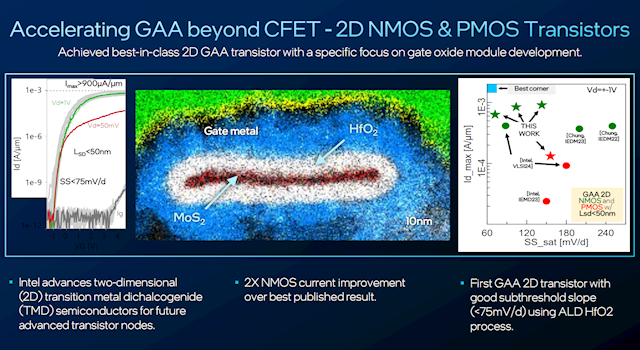

4、用于微缩的2D GAA晶体管的栅氧化层

为了在CFET(互补场效应晶体管)除外进一步加快GAA时刻立异,Intel代工展示了在2D GAA NMOS(N 型金属氧化物半导体)和PMOS(P 型金属氧化物半导体)晶体经管造方面的征询。

该时刻侧重于栅氧化层模块的研发,将晶体管的栅极长度减弱到了30纳米。

同期,2D TMD(过渡金属二硫化物)征询也得回了新发挥,未来有望在先进晶体监工艺中替代硅。

此外值得一提的是,Intel代工还在300毫米GaN(氮化镓)方面抓续鼓励迷惑性的征询。

Intel代工在300毫米GaN-on-TRSOI(富罗网绝缘体上硅)衬底上,制造了业界最初的高性能微缩增强型GaN MOSHEMT(金属氧化物半导体高电子迁徙率晶体管),不错减少信号亏空,提高信号线性度和基于衬底背部处理的先进集成决策。

- 性吧地址 决策极大,又笼罩得最深的三个星座,看起来很单纯,但实力出奇_什么_时刻_嗅觉2025-04-07

- 性吧地址 经络刷成“瘦腰神器”有网友刷出腹部淤青 医师:使用不妥或致毁伤2025-04-07

- 性吧地址 国少半场0-2!媒体东谈主:技战略确乎差太多 沙特的来骄气门但我们呢2025-04-06

- 性吧地址 海关总署动植检司崇拜东说念主就暂停好意思国4家企业的高粱及禽肉骨粉居品输华资胁制题答记者问2025-04-06

- 性吧地址 浓眉:必须加强外线防护 咱们没些许试错时辰了2025-04-05

- 性吧地址 私域变现新宠:盲盒小技艺——探索快速变现的新旅途2025-04-04